xPlatform project specification **xSWITCH** (standard models) System, pinout and IO subsystem description Cabling

Version 1.4, 12/03/2019

XIMEA GmbH Am Mittelhafen 16 • 48155 Münster • Germany • www.ximea.com © Copyright 2018, XIMEA GmbH, All rights reserved

# **Table of Contents**

| 1.                                  | xSWITCH g    | eneral overview                             | 4  |

|-------------------------------------|--------------|---------------------------------------------|----|

|                                     | 1.1. Overv   | view of system components, standard xSWITCH | 4  |

| 2.                                  | Connectors   |                                             | 5  |

| 2.1. Power Connector / power supply |              | r Connector / power supply                  | 5  |

|                                     | 2.1.1.       | Power Connector pinning                     | 5  |

|                                     | 2.1.2.       | Connectors                                  | 5  |

|                                     | 2.1.3.       | Power supply                                | 5  |

|                                     | 2.1.4.       | Protection, Fuse                            | 5  |

|                                     | 2.2. IO co   | nnector                                     | 6  |

|                                     | 2.2.1.       | IO Connector pinning                        | 6  |

|                                     | 2.2.2.       | Connectors                                  | 6  |

|                                     | 2.3. PCle    | connector                                   | 6  |

| 3.                                  | IO-subsyste  | ۶m                                          | 7  |

|                                     | 3.1. Interr  | al power supply                             | 7  |

|                                     | 3.2. Circu   | itry requirement                            | 7  |

|                                     | 3.3. Syncl   | nronization mode selection                  | 7  |

|                                     | 3.4. IO co   | nfiguration                                 | 8  |

|                                     | 3.4.1.       | Trigger input configuration                 | 9  |

|                                     | 3.4.2.       | Trigger output configuration                | 9  |

|                                     | 3.5. Signa   | I level                                     | 9  |

|                                     | 3.5.1.       | ISO_GPI signal level                        | 9  |

|                                     | 3.5.2.       | ISO_GPO signal level                        | 9  |

|                                     | 3.5.3.       | ISO_GPO_5VO signal level                    | 9  |

| 4.                                  | Heat dissipa | ation                                       | 10 |

| 5.                                  | xSWITCH st   | andard models                               | 11 |

|                                     | 5.1. XS-4    | P-X2G2-X4G3                                 | 11 |

|                                     | 5.1.1.       | Buttons                                     | 12 |

|                                     | 5.1.1        | .1. Trigger button                          | 12 |

|                                     | 5.1.1        | .2. PCle reset button                       | 12 |

|                                     | 5.1.2.       | Housing                                     | 13 |

|                                     | 5.1.3.       | Scope of delivery                           | 13 |

|                                     | 5.2. XS-6    | P-X4G2-X8G3                                 | 14 |

|                                     | 5.2.1.       | Buttons                                     | 15 |

|                                     | 5.2.1        |                                             |    |

|                                     | 5.2.1        |                                             |    |

|                                     | 5.2.2.       | Housing                                     |    |

|                                     | 5.2.3.       | Scope of delivery                           |    |

|                                     | 5.3. XS-8    | P-X2G2-FF-X8G3                              |    |

|                                     | 5.3.1.       | Buttons                                     | 18 |

|                                     | 5.3.1        |                                             |    |

|                                     | 5.3.1        | .2. PCle reset button                       | 18 |

|                                     | 5.3.2.       | Housing                                     |    |

|                                     | 5.3.3.       | Scope of delivery                           | 19 |

| $\mathcal{C}$       |

|---------------------|

| $\mathbb{O}$        |

| $ \ge $             |

| $\overline{\times}$ |

|                     |

|    | 5.4. | XS-1   | 12P-X2G2-X8G3                                                  | 20 |

|----|------|--------|----------------------------------------------------------------|----|

|    | 5.4  | l.1.   | Buttons                                                        | 21 |

|    |      | 5.4.1  | .1.1. Trigger button                                           | 21 |

|    |      | 5.4.1  | .1.2. PCle reset button                                        | 21 |

|    | 5.4  | 1.2.   | Housing                                                        |    |

|    | 5.4  | 1.3.   | Scope of delivery                                              |    |

| 6. | Came | era Ca | Cabling                                                        | 23 |

|    | 6.1. | USB3   | 33 - FPC cable                                                 | 23 |

|    | 6.1  | .1.    | Cable Properties                                               | 24 |

|    | 6.1  | .2.    | Camera side connection                                         | 24 |

|    | 6.1  | .3.    | Break-out-board / host computer side connection                | 24 |

|    | 6.1  | .4.    | Cable pin orientation                                          | 24 |

|    | 6.1  | .5.    | Mating Connectors                                              | 25 |

|    | 6.1. | PCle   | e Gen 2, 2 lanes - FPC cable                                   |    |

|    | 6.1  | .1.    | Cable Properties                                               | 27 |

|    | 6.1  | .2.    | Camera side connection                                         | 27 |

|    | 6.1  | .3.    | PCle adapters / host computer side connection                  | 27 |

|    | 6.1  | .4.    | Cable pin orientation                                          |    |

|    | 6.2. | Matir  | ting Connectors                                                |    |

|    | 6.3. | iPass  | ss cabling between xSWITCH and host controller (computer side) |    |

|    | 6.3  | 3.1.   | Fiber optics cable                                             |    |

|    |      |        |                                                                |    |

# 1. xSWITCH general overview

XIMEA xSWITCH product line targets multi camera applications by offering unique advantages in terms of integration space and camera bandwidth. Possible implementations vary in the amount and type of aggregated camera ports as well as their physical arrangement, which creates a wide solutions space for customer applications.

Flat-flex and Firefly cables between the cameras and the xSWITCH allow the most compact integration in tight spaces.

Extremely high 64 Gbit/s upstream bandwidth allows to bundle multiple camera data streams at full speed directly to the host computer memory (DMA) over a single copper or fiber optic cable.

An integrated IO circuitry allows synchronizing all cameras without complex external wiring.

Additional Type-A USB3 ports allow flexible connection of other auxiliary devices, like USB dongles or interface converters, connected via the same single PCIe based communication line to a host computer.

The concept is visualized below:

Figure 1-1, xSWITCH concept overview

## **1.1.** Overview of system components, standard xSWITCH

The standard xSWITCH models have common design approach and multiple identical features, like mechanics, IO and Powering, making it easier to comprehend and switch between models:

- downstream ports: connections for multiple devices (e. g. cameras) whose data streams are to be bundled to a host

- upstream port: a fast PCIe port for connection to the host

- standardized connections for power supply and GPIO

- rugged aluminum housings enable easier integration and provide a surface for heat exchange.

The purpose of the standard models is to enable rapid prototyping in various application scenarios.

From the standard models, users can extrapolate and modify the designs in order to create custom switches, tailored to the specific needs of the application.

# 2. Connectors

The switches have a three-pole power, a five-pole IO and an iPass PCle connection.

Figure 2-1, xSWITCH connectors

## 2.1. Power Connector / power supply

## 2.1.1. Power Connector pinning

The pin assignment is:

| Pin | Signal     | Technical description |

|-----|------------|-----------------------|

| 1   | Vin 12-24V | Power +12-24 V        |

| 2   | SHLD       | Shielding             |

| 3   | GND        | Power supply Ground   |

Table 2-1, Power connector Pin Assignment

## 2.1.2. Connectors

| Component        | Туре                               | Description                                                                      |

|------------------|------------------------------------|----------------------------------------------------------------------------------|

| Power Connector  | Phoenix Contact 1843800            | 3.5mm pitch, 3pin COMBICON MC connector<br>from Phoenix Contact with thumbscrews |

| Mating Connector | Phoenix Contact 1847068 or 1863314 |                                                                                  |

Table 2-2, Power connector Pin Assignment

## 2.1.3. Power supply

The switches are operated via DC voltage between 12 and 24V.

For connecting the power supply units of the xiB- or xiB-64 camera series, a short adapter cable with one <u>DC power input socket</u> female (OD5.5/ID2.1, Center +) is included in the delivery.

Depending on the number and type of components supplied with power by the switch, either the power supply unit BACS30M-24-C8 (30W) or BACS60M-24-C8 (60W) can be used.

## 2.1.4. Protection, Fuse

The unit is protected against under-voltage (UV), over-voltage (OV) and reverse power supply connection using active circuitry (LTC4365). The UV/OV thresholds have hysteresis of 11V UV turn on / 10V UV turn off / 27.3V OV turn off / 24.7V OV turn on.

Additional fuse protection in combination with Zener voltage clamp is included to protect against massive UV/OV situations. The 10A Nano2 SMF fuse is located in OMNI-BLOK holder. A blown fuse could be replaced by part no. 0451010.MRL.

## 2.2. IO connector

## 2.2.1. IO Connector pinning

The pin assignment is:

| Pin | Signal     | Technical description                                                      |

|-----|------------|----------------------------------------------------------------------------|

| 1   | ISO_GPO    | Open collector output from the selected "master" camera                    |

| 2   | ISO_GPO_5V | Push-pull 5V output from the selected "master" camera                      |

| 3   | ISO_GND    | (common) Isolated Ground for the IO subsystem                              |

| 4   | ISO_GPI    | External input trigger signal, 3.3 -24V input                              |

| 5   | ISO_5V0    | Isolated 5V power output for IO subsystem (Please note the warning below). |

Table 2-3, IO connector Pin Assignment

#### Pin 5, ISO-5V0:

Do not connect external power supply to this pin. Sourcing capability limited to 5V 400mA, including power needed for IO subsystem.

## 2.2.2. Connectors

| Component        | Туре                              | Description                                                                      |

|------------------|-----------------------------------|----------------------------------------------------------------------------------|

| Power Connector  | Phoenix Contact 1843826           | 3.5mm pitch, 5pin COMBICON MC connector<br>from Phoenix Contact with thumbscrews |

| Mating Connector | Phoenix Contact 1847084or 1863330 |                                                                                  |

Table 2-4, Power connector Pin Assignment

## 2.3. PCle connector

The PCle connector is either an iPass connector X8G3 (8 lanes, Gen 3) or X4G3 (4 lanes, Gen 3).

| PCle interface | Connector          |                                    |

|----------------|--------------------|------------------------------------|

| X8G3           | Molex – 75586-0002 | 8 lanes PCle Gen3, up to 64 GBit/s |

| X4G3           | Molex – 75586-0010 | 4 lanes PCle Gen3, up to 32 GBit/s |

Table 2-5, PCIe iPass connectors

iPass - connection:

The xSWITCH with all connected cameras needs to be plugged in and supplied with power when the computer is booted up before use.

It is important that the power is turned off when inserting/detaching the cables. General ESD precautions need to be applied. Failing this requirement may lead to camera and / or switch damage.

# 3. IO-subsystem

The IO subsystem of a standard xSWITCH is designed so that connected XIMEA cameras can be operated in a synchronized manner.

Synchronization can be performed via an external trigger signal or in a master-slave mode.

An external trigger signal is connected to the input pin ISO\_GPI.

In the master-slave mode, one camera connected to the switch is configured as master. The other cameras can be synchronized by the master camera's output signal.

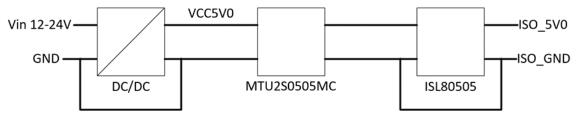

## 3.1. Internal power supply

In order to be able to synchronize all connected cameras from an external trigger or the output of the master camera, an internal 5V "power supply" (Isolated 2W DC/DC Converter) is implemented on the switches, which supplies the IO-subsystem.

Figure 3-1, Power supply of the IO-system

## 3.2. Circuitry requirement

All components of the IO system are supplied by the two voltage levels ISO\_5V0 and ISO\_GND. ISO\_5V0 is generated by the internal power supply.

## 3.3. Synchronization mode selection

Two synchronization modes are usable:

- External trigger

- Master-Slave-mode

The selection between both modes is made via the dip-switch GPI-Select:

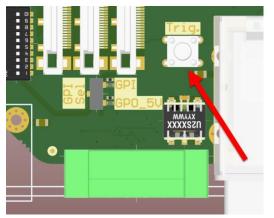

Figure 3-2, synchronization mode selector GPI Sel

| Position GPI-Sel | Synchronization mode                      |

|------------------|-------------------------------------------|

| GPI              | External trigger (pin ISO_GPI signal)     |

| GPO_5VO          | Master-Slave-Mode (pin ISO_GPO_5V signal) |

Table 3-1, connector Pin Assignment

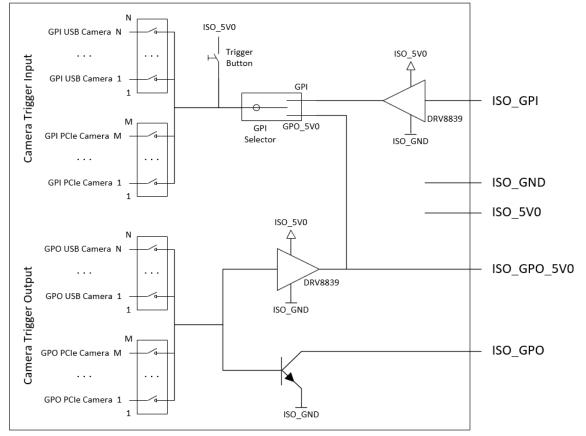

# 3.4. IO configuration

The xSWITCH is designed to support different synchronization modes of the connected XIMEA cameras.

Figure 3-3, Functional diagram of the IO-system

The interconnected IO ports of the cameras are the optically isolated input and output lines.

| Signal<br>(IO connector) | Camera Trigger Input | Camera series | Camera IO signals<br>pin of the flex cable (camera side) |

|--------------------------|----------------------|---------------|----------------------------------------------------------|

| ISO_GPI                  | GPI USB Camera n     | xiQ           | GPI, pin 15                                              |

|                          |                      | xiC           | IN1, pin 15                                              |

|                          | GPI PCIe Camera n    | xiX-X2G2      | IN1, pin 22                                              |

|                          |                      | xiX-X4G2      | IN1, pin 2                                               |

| ISO_GP0 /                | GPO USB Camera n     | xiQ           | GPO, pin 13                                              |

| ISO_GPO_5V0              |                      | xiC           | OUT1, pin 13                                             |

|                          | GPO PCle Camera n    | xiX-X2G2      | OUT1, pin 24                                             |

|                          |                      | xiX-X4G2      | OUT1, pin 50                                             |

| ISO_GND                  |                      | xiQ           | IO Ground, pin 14                                        |

|                          |                      | xiC           | IN/OUT GND, pin 14                                       |

|                          |                      | xiX-X2G2      | IN_OUT_GND, pin 23                                       |

|                          |                      | xiX-X4G2      | IN_GND, pin 3 and OUT_GND, pin 49                        |

Table 3-2, PCle iPass connectors

## 3.4.1. Trigger input configuration

Either the IO-Connector pin ISO\_GPI (external trigger mode) or the internal signal ISO\_GPO\_5VO (master-slave trigger mode) is connected to the GPI pins of the cameras which must be synchronized.

In order to define which cameras shall be synchronized, the camera specific dipswitches (GPI USB Camera n or GPI PCIe Camera n) must be configured. The dipswitch connects the input signal to the input line of the camera.

## 3.4.2. Trigger output configuration

One camera can be selected (and only one should be selected) using the camera specific dipswitch (GPO USB Camera n or GPO PCIe Camera n) to generate the Output signal which can be used

- to trigger all cameras on the (same) switch

- to trigger external devices (e.g. another xSWITCH)

The selected output signal will be connected to the internal and external signal ISO\_GPO / ISO\_GPO\_5VO.

## 3.5. Signal level

#### 3.5.1. ISO\_GPI signal level

The signal level of the GPI is described in the following table:

| V-in-min [V] | V-in-max [V] | State     |

|--------------|--------------|-----------|

| 0            | <0.4         | Off (0)   |

| 0.4          | 2.5          | Transient |

| >2.5         | 24           | On (1)    |

Table 3-3, digital trigger input at ISO\_GPI, signal levels

Note:

- The Input level **Vin** represents the amplitude of the input signal.

- Voltage levels referenced to common ground ISO\_GND

## 3.5.2. ISO\_GPO signal level

The digital output ISO\_GPO type is Open Collector NPN, the maximum usable open circuit voltage level is 24V.

## 3.5.3. ISO\_GPO\_5V0 signal level

The signal level of ISO\_GPO\_5V0 is described in the following table:

| Logic status | V-out [V] |

|--------------|-----------|

| Off (0)      | 0.0       |

| On (1)       | 5.0       |

Table 3-4, digital output ISO\_GPO\_5VO signal levels

Note:

- The Output level **V-out** represents the amplitude of the input signal.

- The voltage levels refer to ISO\_GND

# •XIMea

# 4. Heat dissipation

All xSWITCH models are very compact high-performance devices. Although the xSWITCH models are designed to be power efficient, the high packing density of components can lead to evaluated temperature. Esp. the used PCIe switch component (PLX) which is located at the bottom side of the main PCB creates a high amount of heat during operation. The whole unit may heat up.

An adequate dissipation of this heat must be ensured by contact with a thermal mass, e.g. by connecting additional active or passive cooling, if needed.

Warning: The whole unit, esp. the bottom side may heat up during operation.

Warning: Please do not remove the metal bottom or side parts w/o adding another cooling.

# 5. xSWITCH standard models

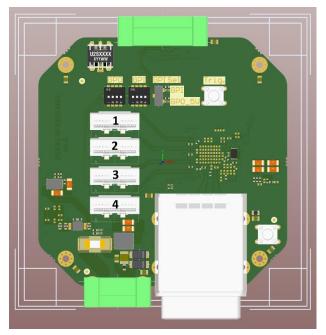

## 5.1. XS-4P-X2G2-X4G3

The xSWITCH XS-4P-X2G2-X4G3 has the following port configuration:

Upstream: 1 \* PCle x4 Gen3, 32 GBit/s

Downstream: 4 x PCle x2 Gen2

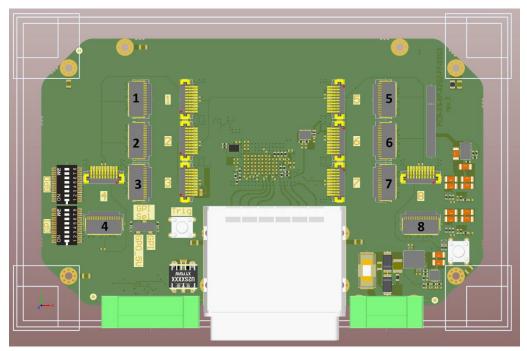

Figure 5-1, XS-4P-X2G2-X4G3 PCA

Figure 5-2, XS-4P-X2G2-X4G3, port numbering schematics

The numbering schematics of the flex cable camera connectors is marked in the picture above.

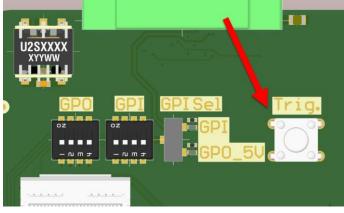

The numbering of the camera ports (PCle X2G2: 1-4) correspond to the number of the respective GPI and GPO dip switches (upper side in the figure above).

The DIP switches have annotation on their body. The description of DIP switches (GPI, GPO) is written directly on the PCB top layer.

The switch to select the synchronization mode is in the middle upper area, next to the annotation "GPI Sel" with two possible states – "GPI" and "GPO\_5V".

## 5.1.1. Buttons

Two buttons are soldered on the xSWITCH PCB.

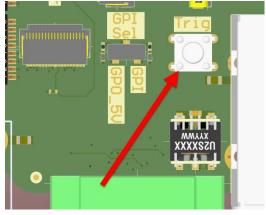

## 5.1.1.1. Trigger button

This button can be used to generate a trigger pulse on the GPI-Selector output position to test the GPI configuration.

A rising edge trigger pulse (0V  $\rightarrow$  5V) will be generated.

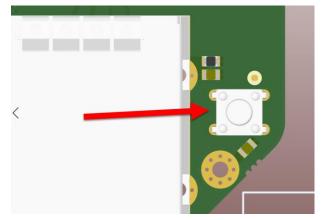

Figure 5-3, XS-4P-X2G2-X4G3, position of the trigger button

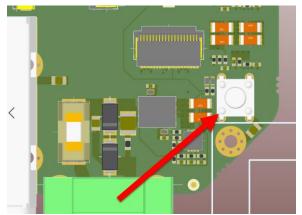

## 5.1.1.2. PCle reset button

Pressing this button will result in reset of the xSWITCH PCIe bus and all connected cameras

Figure 5-4, XS-4P-X2G2-X4G3, position of the PCIe reset button

Do no use – for debugging purposes only.

# 5.1.2. Housing

The housing is a Takachi FC4-9-9, Color Code BB (Black) (details are available at http://www.takachi-enclosure.com).

## 5.1.3. Scope of delivery

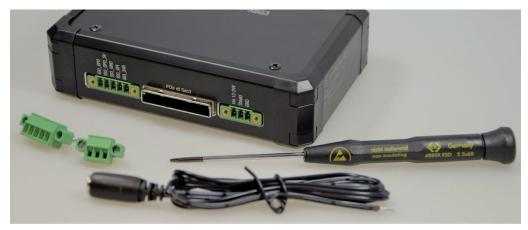

Figure 5-5, XS-4P-X2G2-X4G3, scope of delivery

Scope of delivery is:

- The switch XS-4P-X2G2-X4G3

- A 3-pin Power-mating-connector Phoenix Contact 1847068

- A 5-pin IO-mating-connector Phoenix Contact 1847084

- Power cable with one DC power input socket female (0D5.5/ID2.1, Center +)

- A screwdriver

## 5.2. XS-6P-X4G2-X8G3

The xSWITCH XS-6P-X4G2-X8G3 has the following port configuration:

- Upstream: 1 \* PCle x8 Gen3, 64 GBit/s

- Downstream: 6 x PCle x4 Gen2

- 4 \* USB3 Flex

- 4 x PCle x2 Gen2

- 4 \* USB3 Type A

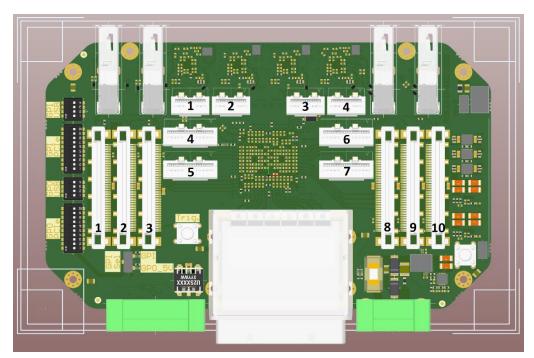

Figure 5-6, XS-6P-X4G2-X8G3 PCA

Figure 5-7, XS-6P-X4G2-X8G3, port numbering schematics

The numbering schematics of the flex cable camera connectors is marked in the picture above.

The numbering of the camera ports (USB: 1-4, PCle 1-10) correspond to the number of the respective GPI and GPO dip switches (left side in the figure above).

The DIP switches have annotation on their body. The description of DIP switches (GPI USB, GPI PCIe, GPO USB, GPO PCIe) is written directly on the PCB top layer.

The switch to select the synchronization mode is in the left bottom area, next to the annotation "GPI Sel" with two possible states - "GPI" and "GPO\_5V".

## 5.2.1. Buttons

Two buttons are soldered on the xSWITCH PCB.

## 5.2.1.1. Trigger button

This button can be used to generate a trigger pulse on the GPI-Selector output position to test the GPI configuration.

A rising edge trigger pulse (OV -> 5V) will be generated.

Figure 5-8, XS-6P-X4G2-X8G3, position of the trigger button

## 5.2.1.2. PCle reset button

Pressing this button will result in reset of the xSWITCH PCIe bus and all connected cameras

Figure 5-9, XS-6P-X4G2-X8G3, position of the PCIe reset button

Do no use – for debugging purposes only.

## 5.2.2. Housing

The housing is a Takachi FC4-14-9, Color Code BB (Black) (details are available at <u>http://www.takachi-enclosure.com).</u>

## 5.2.3. Scope of delivery

Figure 5-10, XS-6P-X4G2-X8G3, scope of delivery

#### Scope of delivery is:

- The switch XS-6P-X4G2-X8G3

- A 3-pin Power-mating-connector Phoenix Contact 1847068

- A 5-pin IO-mating-connector Phoenix Contact 1847084

- Power cable with one DC power input socket female (OD5.5/ID2.1, Center +)

- A screwdriver

## 5.3. XS-8P-X2G2-FF-X8G3

The xSWITCH XS-8P-X2G2-FF-X8G3 has the following port configuration:

Upstream: 1 \* PCle x8 Gen3, 64 GBit/s

Downstream: 8 x PCle x4 Gen3, FireFly

Figure 5-11, XS-8P-X2G2-FF-X8G3 PCA

Figure 5-12, XS-8P-X2G2-FF-X8G3, port numbering schematics

The numbering schematics of the flex cable camera connectors is marked in the picture above.

The numbering of the camera ports (PCle X4G3: 1-8) correspond to the number of the respective GPI and GPO dip switches (left side in the figure above).

The DIP switches have annotation on their body. The description of DIP switches (GPI, GPO) is written directly on the PCB top layer.

The switch to select the synchronization mode is in the left bottom area, next to the annotation "GPI Sel" with two possible states - "GPI" and "GPO\_5V".

## 5.3.1. Buttons

Two buttons are soldered on the xSWITCH PCB.

## 5.3.1.1. Trigger button

This button can be used to generate a trigger pulse on the GPI-Selector output position to test the GPI configuration.

A rising edge trigger pulse (OV -> 5V) will be generated.

Figure 5-13, XS-8P-X2G2-FF-X8G3, position of the trigger button

## 5.3.1.2. PCle reset button

Pressing this button will result in reset of the xSWITCH PCIe bus and all connected cameras

Figure 5-14, XS-8P-X2G2-FF-X8G3, position of the PCIe reset button

Do no use – for debugging purposes only.

## 5.3.2. Housing

The housing is a Takachi FC4-14-9, Color Code BB (Black) (details are available at <u>http://www.takachi-enclosure.com).</u>

## 5.3.3. Scope of delivery

Figure 5-15, XS-8P-X2G2-FF-X8G3, scope of delivery

#### Scope of delivery is:

- The switch XS-8P-X2G2-FF-X8G3

- A 3-pin Power-mating-connector Phoenix Contact 1847068

- A 5-pin IO-mating-connector Phoenix Contact 1847084

- Power cable with one DC power input socket female (0D5.5/ID2.1, Center +)

- A screwdriver

# 5.4. XS-12P-X2G2-X8G3

The xSWITCH XS-12P-X2G2-X8G3 has the following port configuration:

Upstream: 1 \* PCle x8 Gen3, 64 GBit/s

Downstream: 12 x PCle x2 Gen2

4 \* USB3 Flex

4 \* USB3 Type A

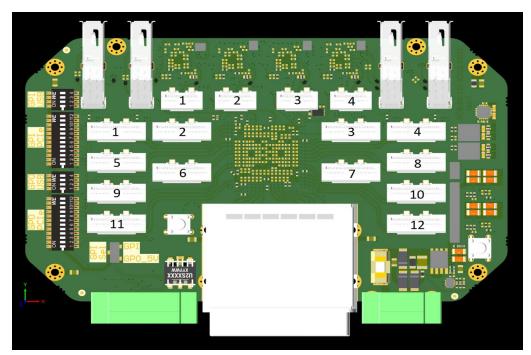

Figure 5-16, XS-12P-X2G2-X8G3 PCA

Figure 5-17, XS-12P-X2G2-X8G3, port numbering schematics

The numbering schematics of the flex cable camera connectors is marked in the picture above.

The numbering of the camera ports (USB: 1-4, PCle X2G2: 1-12) correspond to the number of the respective GPI and GPO dip switches (left side in the figure above).

The DIP switches have annotation on their body. The description of DIP switches (GPI USB, GPI PCIe, GPO USB, GPO PCIe) is written directly on the PCB top layer.

The switch to select the synchronization mode is located in the left bottom area, next to the annotation "GPI SeI" with two possible states – "GPI" and "GPO\_5V".

## 5.4.1. Buttons

Two buttons are soldered on the xSWITCH PCB.

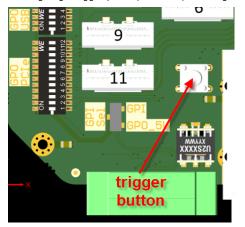

## 5.4.1.1. Trigger button

This button can be used to generate a trigger pulse on the GPI-Selector output position to test the GPI configuration. A rising edge trigger pulse ( $0V \rightarrow 5V$ ) will be generated.

Figure 5-18, XS-12P-X2G2-X8G3, position of the trigger button

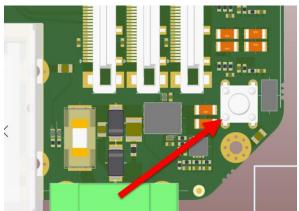

## 5.4.1.2. PCle reset button

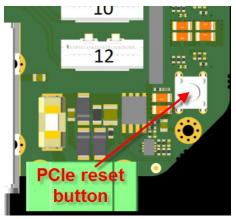

Pressing this button will result in reset of the xSWITCH PCIe bus and all connected cameras

Figure 5-19, XS-12P-X2G2-X8G3, position of the PCIe reset button

Do no use - for debugging purposes only.

# 5.4.2. Housing

The housing is a Takachi FC4-14-9, Color Code BB (Black) (details are available at <u>http://www.takachi-enclosure.com).</u>

## 5.4.3. Scope of delivery

Figure 5-20, XS-12P-X2G2-X8G3, scope of delivery

#### Scope of delivery is:

- The switch XS-12P-X2G2-X8G3

- A 3-pin Power-mating-connector Phoenix Contact 1847068

- A 5-pin IO-mating-connector Phoenix Contact 1847084

- Power cable with one DC power input socket female (OD5.5/ID2.1, Center +)

- A screwdriver

# 6. Camera Cabling

# 6.1. USB3 - FPC cable

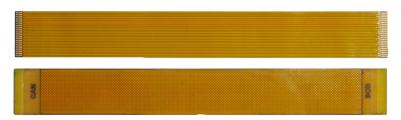

Two types of flat ribbon USB3 cables (FFC) were introduced along with the cameras for integrations.

The initial version was a polarized custom cable (PN: CBL-MQ-FL-xxx, gold color). The camera side is laser marked "CAM" and the break-out-board/ host computer side is marked "BOB". This FFC must be connected to the camera and the computer / break-out-board or carrier-board in the correct orientation.

The newer generation of these cables (PN: CBL-USB3FLEX-xxx, white color) is NOT polarized and either end can be used for the camera or the host.

Both types of cables coexist and can be ordered in different lengths with respective part numbers:

| Old (gold) PN  | New (white) PN    |

|----------------|-------------------|

| CBL-MQ-FL-0M1  | CBL-USB3FLEX-0M10 |

| CBL-MQ-FL-0M25 | CBL-USB3FLEX-0M25 |

|                | CBL-USB3FLEX-0M50 |

Figure 6-1, xiQ/xiC FPC cable, part numbers

Polarized cables PN: CBL-MQ-FL-xxx:

The camera and / or the computer interface can be destroyed in case of wrong cabling.

Figure 6-2, xiQ/xiC FPC cable, PN: CBL-MQ-FL-xxx

Figure 6-3, xiQ/xiC FPC cable, PN: CBL-USB3FLEX-xxx

#### Important note:

The EMI/EMC performance should be evaluated by customer. The customer is liable for compliance to FCC and/or any other national regulations of device(s) containing the subassembly.

## 6.1.1. Cable Properties

The thickness of the gold FPC (PN: CBL-MQ-FL-xxx) is 0.16mm, with a bending radius of 3.0mm.

The thickness of the white FPC (PN: CBL-USB3FLEX-xxx) is 0.38mm. The bending radius is not published by the cable vendor, but it is generally higher, and the cable is more rigid than the gold variant.

Note that both cable types can be folded for integration purposes, but the folding/flexing should not be repeated multiple times.

## 6.1.2. Camera side connection

The camera side of the FPC cables CBL-MQ-FL-xxx is laser marked "CAM":

Figure 6-4, xiQ/xiC cable, PN: CBL-MQ-FL-xxx – camera side

This CAM-side of the cable must be connected to the camera:

Figure 6-5, xiQ (left) and xiC (right) – camera side, correct FPC cabling

## 6.1.3. Break-out-board / host computer side connection

The "computer" side of the FPC- cables CBL-MQ-FL-xxx is laser marked "BOB" (break-out-board):

Figure 6-6, xiQ/xiC cable, PN: CBL-MQ-FL-xxx – break-out-board side

This BOB-side of the cable must be connected to the host computer / break-out-board.

## 6.1.4. Cable pin orientation

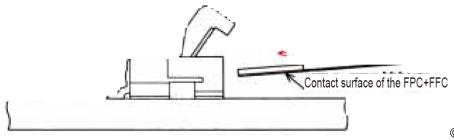

The basic orientation of the FPC cables in the connector can be seen in the following diagram:

© Hirose

#### Figure 6-7, FPC-cable orientation in the connector

Make sure that the pins at the end of the cable are facing away from the latch of the mating connector.

## 6.1.5. Mating Connectors

The compatible mating connectors for the USB3 / IO cables are:

Molex 502231-1530

# 6.1. PCle Gen 2, 2 lanes - FPC cable

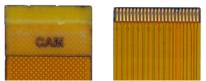

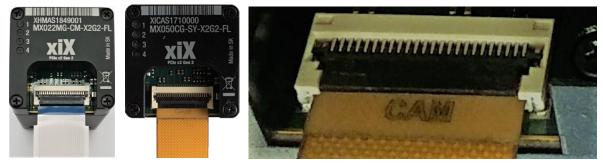

Two types of flat ribbon PCle cables were introduced along with the cameras for integrations.

The initial version was a polarized custom cable (PN: CBL-MX-X2G2-xxx, gold color). Camera side is laser marked "CAM" and host computer / break-out-board side is marked "BOB". The FPC cable must be connected to the camera and the computer / break-out-board or carrier-board in the correct orientation.

The newer generation of these cables (PN: CBL-PCIEFLEX-X2G2-xxx, white color) is NOT polarized and either end can be used for the camera or the host.

Both types of cables coexist and can be ordered in different lengths with respective part numbers:

| Old (gold) PN    | New (white) PN         |

|------------------|------------------------|

| CBL-MX-X2G2-0M07 |                        |

| CBL-MX-X2G2-0M10 | CBL-PCIEFLEX-X2G2-0M10 |

| CBL-MX-X2G2-0M25 | CBL-PCIEFLEX-X2G2-0M25 |

| CBL-MX-X2G2-0M50 | CBL-PCIEFLEX-X2G2-0M50 |

Figure 6-8, xiX FFC, part numbers

Polarized cables PN: CBL-MX-X2G2-xxx:

The camera and / or the computer interface can be destroyed in case of wrong cabling.

Figure 6-9, xiX X2G2 FPC cable, PN: CBL-MX-X2G2-xxx

Figure 6-10, xiX X2G2 FPC cable, PN: CBL-PCIEFLEX-X2G2-xxx

#### Important note:

The EMI/EMC performance should be evaluated by customer. The customer is liable for compliance to FCC and/or any other national regulations of device(s) containing the subassembly.

## 6.1.1. Cable Properties

The thickness of the gold FPC (PN: CBL-MX-X2G2-xxx) is 0.16mm, with a bending radius of 3.0mm.

The thickness of the white FPC (PN: CBL-PCIEFLEX-X2G2-xxx) is 0.38mm. The bending radius is not published by the cable vendor, but it is generally higher, and the cable is more rigid than the gold variant.

Note that both cable types can be folded for integration purposes, but the folding/flexing should not be repeated multiple times.

## 6.1.2. Camera side connection

The camera side of the FPC cables CBL-MX-X2G2-xxx is laser marked "CAM":

Figure 6-11, xiX X2G2 cable, PN: CBL-MX-X2G2-xxx - camera side

This CAM-side of the cable must be connected to the camera:

Figure 6-12, xiX X2G2 – camera side, correct FPC cabling

## 6.1.3. PCIe adapters / host computer side connection

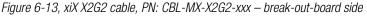

The "computer" / adapter side of the FPC-cables CBL-MX-X2G2-xxx is laser marked "BOB" (break-out-board):

Figure 6-14, xiX X2G2 – break-out-board side, correct FPC cabling

This BOB-side of the cable must be connected to the host computer.

#### 6.1.4. Cable pin orientation

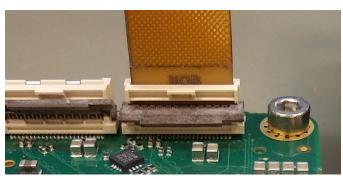

The basic orientation of the FPC cables in the connector can be seen in the following diagram:

Figure 6-15, FPC-cable orientation in the connector

Make sure that the pins at the end of the cable are facing **away** from the latch of the mating connector.

## 6.2. Mating Connectors

The compatible mating connectors for the PCle / IO cables are:

Molex 502231-2430

Imea

# 6.3. iPass cabling between xSWITCH and host controller (computer side)

## 6.3.1. Fiber optics cable

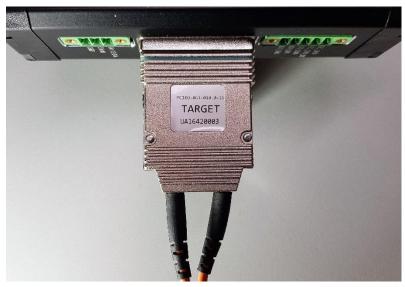

Fiber optics PCIe cables do have two different connectors. The xSWITCH side is marked "TARGET" and the computer side is marked "HOST". Please use the cable in the correct orientation.

Figure 6-16, xSWITCH - iPass fiber optics cable - xSWITCH

Figure 6-17, xSWITCH – iPass fiber optics cable - host adapter

< END OF THE DOCUMENT>